Trạm làm lại BGA quang tự động

Được sử dụng rộng rãi trong sửa chữa ở cấp độ chip cho bo mạch chủ của điện thoại di động, máy tính xách tay, máy tính, TV, máy điều hòa không khí, v.v. Nó có tỷ lệ sửa chữa thành công cao và mức độ tự động hóa cao và tiết kiệm rất nhiều công sức của con người. Chúng tôi là nhà sản xuất chuyên nghiệp của máy này và có sẵn máy này trong kho.

Mô tả

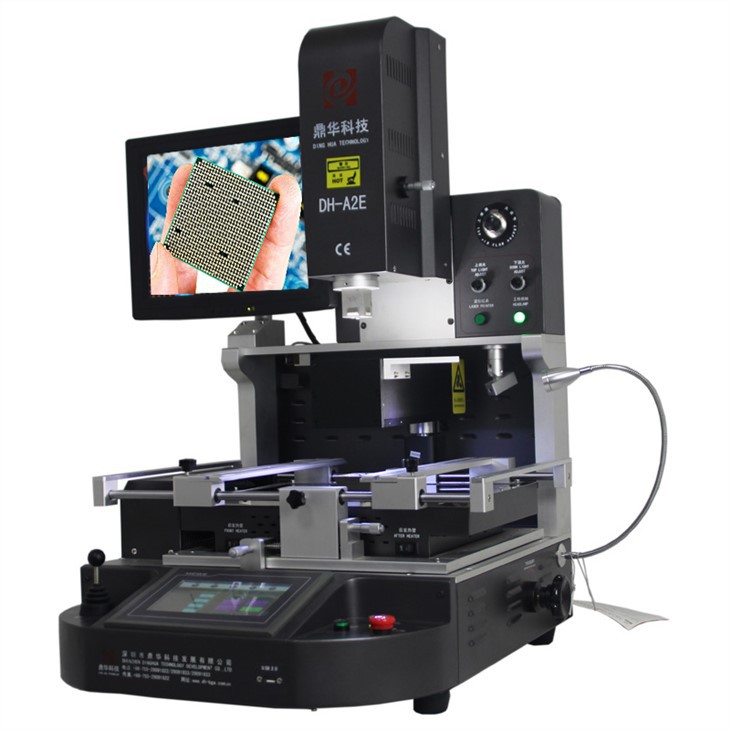

Trạm làm lại BGA quang tự động

1.Ứng dụng Trạm làm lại BGA quang tự động

Bo mạch chủ của máy tính, điện thoại thông minh, máy tính xách tay, bảng logic MacBook, máy ảnh kỹ thuật số, điều hòa không khí, TV và các thiết bị điện tử khác

thiết bị từ ngành y tế, công nghiệp truyền thông, công nghiệp ô tô, v.v.

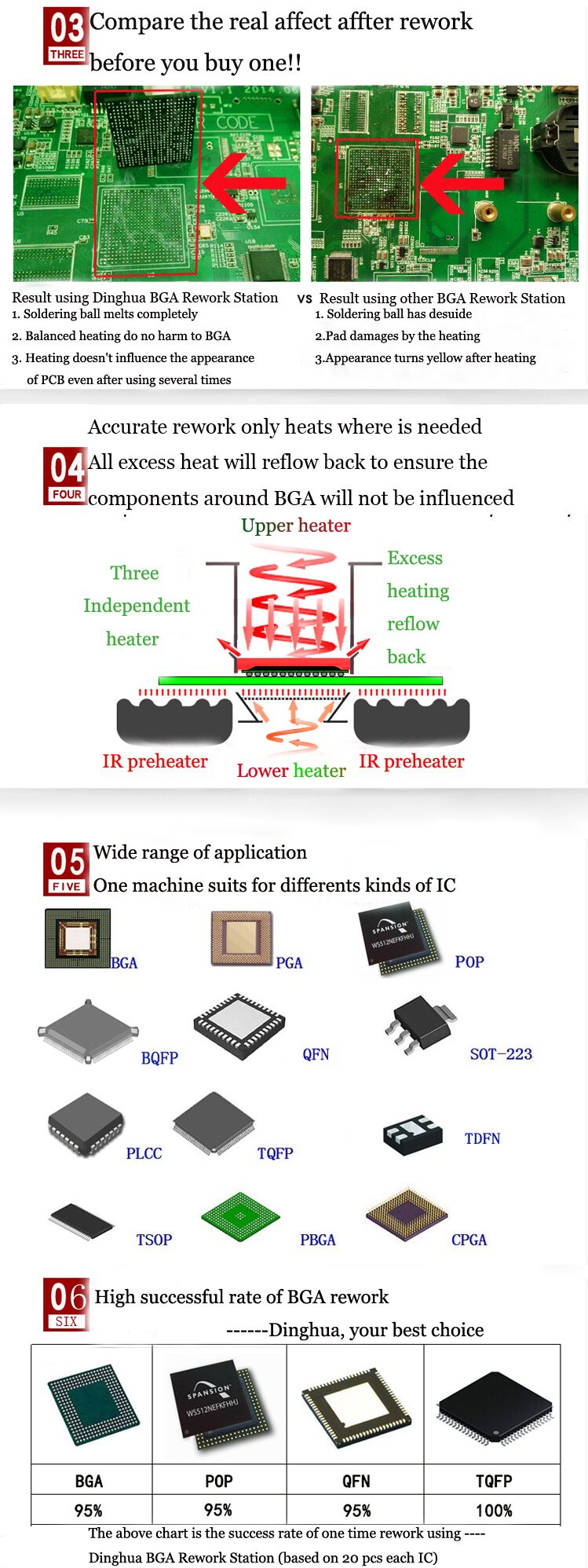

Thích hợp cho các loại chip khác nhau: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, chip LED.

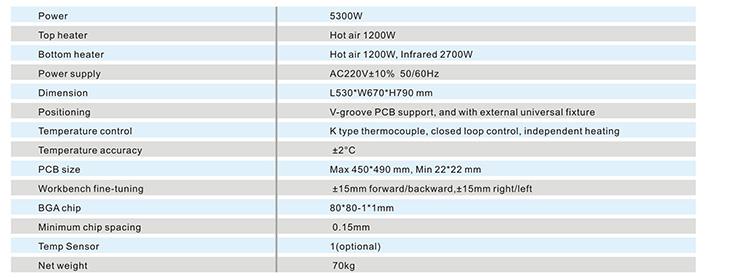

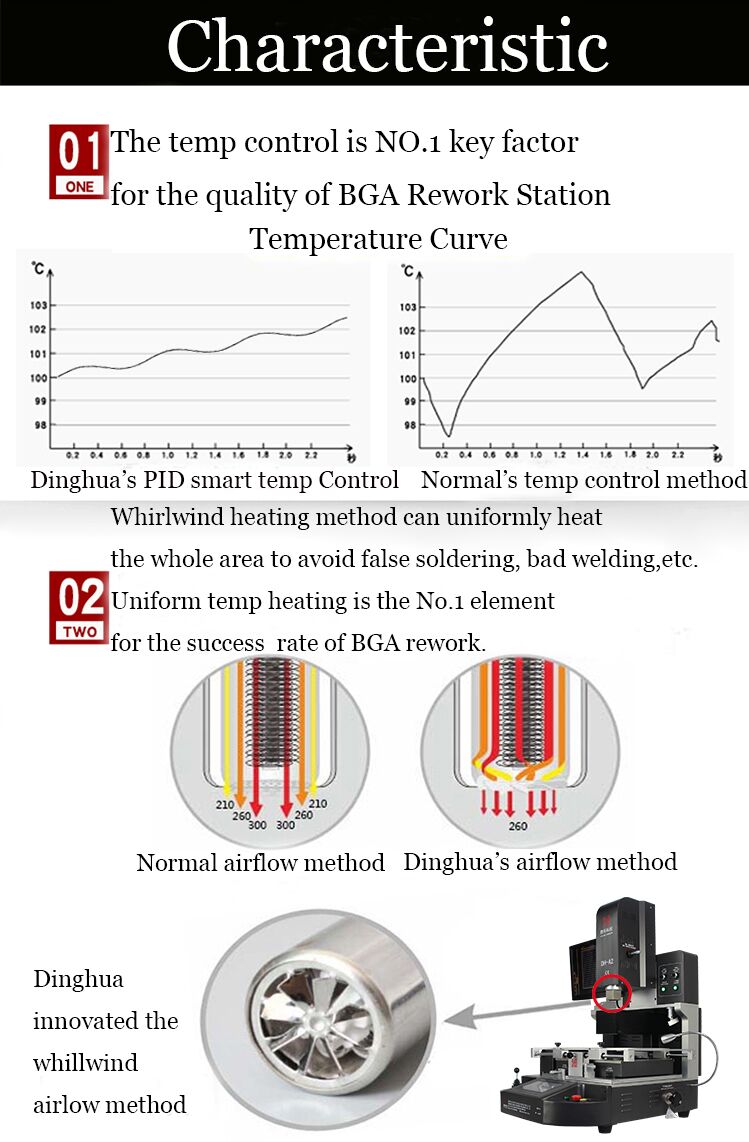

2. Tính năng sản phẩm của Trạm làm lại BGA quang tự động

• Tỷ lệ sửa chữa thành công ở cấp độ chip cao. Quá trình hàn, lắp và hàn là tự động.

• Căn chỉnh chính xác mọi mối hàn có thể được đảm bảo với camera CCD căn chỉnh quang học.

• Có thể đảm bảo kiểm soát nhiệt độ chính xác với 3 vùng gia nhiệt độc lập. Máy có thể thiết lập và lưu

1 triệu hồ sơ nhiệt độ.

• Tích hợp chân không trong đầu gắn tự động lấy chip BGA sau khi hoàn thành quá trình khử hàn.

3.Đặc điểm của trạm làm lại BGA quang tự động

4. Chi tiết về Trạm làm lại BGA quang tự động

camera CCD (hệ thống căn chỉnh quang học chính xác); Màn hình kỹ thuật số 2.HD; 3. Panme (chỉnh góc phoi);

4.3 máy sưởi độc lập (khí nóng & tia hồng ngoại); 5. Định vị laze; 6. Giao diện màn hình cảm ứng HD, điều khiển PLC;

7.Đèn pha Led; 8. Điều khiển cần điều khiển.

5. Tại sao chọn Trạm làm lại BGA quang tự động của chúng tôi?

6. Giấy chứng nhận Trạm làm lại BGA quang tự động

7. Đóng gói & Vận chuyển Trạm làm lại BGA quang tự động

8.HỎI ĐÁP

Làm thế nào để kiểm tra chip?

Thử nghiệm chip cấp hệ thống ban đầu

SoC dựa trên các quy trình submicron sâu, vì vậy việc thử nghiệm các thiết bị Soc mới đòi hỏi một cách tiếp cận hoàn toàn mới. Bởi vì mỗi thành phần chức năng

có yêu cầu thử nghiệm riêng, kỹ sư thiết kế phải lập kế hoạch thử nghiệm sớm trong quá trình thiết kế.

Kế hoạch kiểm tra từng khối cho các thiết bị SoC phải được triển khai: các công cụ ATPG được định cấu hình phù hợp để kiểm tra logic; thời gian thử nghiệm ngắn; tốc độ cao mới

các mô hình lỗi và kiểm tra nhiều bộ nhớ hoặc mảng nhỏ. Đối với dây chuyền sản xuất, phương pháp chẩn đoán không chỉ tìm ra lỗi mà còn phân tách

nút bị lỗi từ nút làm việc. Ngoài ra, các kỹ thuật ghép kênh thử nghiệm nên được sử dụng bất cứ khi nào có thể để tiết kiệm thời gian thử nghiệm. Trong lĩnh vực cao

kiểm tra IC tích hợp, các kỹ thuật thiết kế có thể kiểm tra của ATPG và IDDQ có cơ chế phân tách lỗi mạnh mẽ.

Các tham số thực tế khác cần được lên kế hoạch trước bao gồm số lượng chân cần được quét và dung lượng bộ nhớ ở mỗi đầu chân.

Quét ranh giới có thể được nhúng trên SoC, nhưng không giới hạn ở các thử nghiệm kết nối trên bo mạch hoặc mô-đun nhiều chip.

Mặc dù kích thước chip ngày càng giảm nhưng một con chip vẫn có thể chứa hàng triệu đến 100 triệu bóng bán dẫn và số lượng chế độ thử nghiệm đã tăng lên chưa từng thấy

cấp độ, dẫn đến chu kỳ thử nghiệm dài hơn. Vấn đề này có thể được kiểm tra. Chế độ nén để giải quyết, tỷ lệ nén có thể đạt 20 phần trăm đến 60 phần trăm. Đối với quy mô lớn ngày nay

thiết kế chip, để tránh các vấn đề về dung lượng, cần phải tìm phần mềm thử nghiệm có thể chạy trên hệ điều hành 64-bit.

Ngoài ra, phần mềm thử nghiệm phải đối mặt với các vấn đề thử nghiệm mới do các quy trình sâu dưới micron gây ra và tần suất ngày càng tăng. Trong quá khứ, chế độ kiểm tra ATPG cho

kiểm tra lỗi chặn tĩnh không còn được áp dụng. Việc thêm các mẫu chức năng vào các công cụ truyền thống khiến việc tìm ra các lỗi mới trở nên khó khăn hơn. Một cách tiếp cận tốt hơn là

phân loại các nhóm chế độ chức năng trong quá khứ để xác định lỗi nào không thể phát hiện được, sau đó tạo chế độ ATPG để nắm bắt các loại lỗi bị thiếu này.

Khi công suất thiết kế tăng lên và thời gian thử nghiệm trên mỗi bóng bán dẫn giảm xuống, để tìm ra các vấn đề liên quan đến tốc độ và xác minh thời gian của mạch, một phương pháp thử nghiệm đồng bộ

phải được tuyển dụng. Thử nghiệm đồng bộ phải kết hợp nhiều mô hình lỗi, bao gồm mô hình nhất thời, độ trễ đường dẫn và IDDQ.

Một số công ty trong ngành tin rằng việc kết hợp các lỗi chặn, chức năng và tạm thời/độ trễ đường dẫn có thể là chiến lược thử nghiệm hiệu quả nhất. cho sâu

chip submicron và hoạt động tần số cao, kiểm tra độ trễ đường dẫn và tạm thời thậm chí còn quan trọng hơn.

Để giải quyết vấn đề về độ chính xác của ATE khi đồng bộ hóa lõi kiểm tra và giảm chi phí, cần phải tìm ra một phương pháp mới giúp đơn giản hóa giao diện của

thiết bị kiểm tra (kiểm tra độ trễ nhất thời và đường dẫn yêu cầu đồng hồ chính xác tại giao diện thiết bị kiểm tra), Nó đảm bảo rằng tín hiệu đủ chính xác trong quá trình kiểm tra.

Do có khả năng cao xảy ra lỗi sản xuất trong khối bộ nhớ SoC nên bộ nhớ BIST phải có chức năng chẩn đoán. Một khi một vấn đề được tìm thấy,

đơn vị địa chỉ bị lỗi có thể được ánh xạ tới bộ nhớ dự phòng của đơn vị địa chỉ dự phòng và địa chỉ lỗi được phát hiện sẽ bị loại bỏ. Tránh loại bỏ

toàn bộ con chip đắt tiền.

Thử nghiệm các khối bộ nhớ nhúng nhỏ giúp loại bỏ nhu cầu về các cổng bổ sung hoặc logic điều khiển. Ví dụ, kỹ thuật kiểm tra chuyển đổi vector có thể chuyển đổi

các chế độ chức năng thành một loạt các chế độ quét.

Không giống như phương pháp BIST, đầu vào chức năng của khối bộ nhớ bỏ qua không yêu cầu logic bổ sung. Vì không cần logic kiểm tra bổ sung, SoC

các kỹ sư phát triển có thể sử dụng lại các mẫu thử nghiệm đã được hình thành trong quá khứ.

Các công cụ ATPG nâng cao không chỉ kiểm tra song song các macro mà còn xác định xem có xung đột hay không, cũng như nêu chi tiết macro nào có thể được kiểm tra song song và macro nào có thể được kiểm tra song song.

macro không thể được kiểm tra song song. Ngoài ra, các macro này có thể được kiểm tra hiệu quả ngay cả khi đồng hồ macro giống với đồng hồ quét (chẳng hạn như bộ nhớ đồng bộ).

Hiện tại, không có đủ điểm kiểm tra trên bảng hai mặt dày đặc và mỗi con chip phức tạp phải được trang bị mạch quét ranh giới. Không có

quét ranh giới, tra cứu lỗi sản xuất ở cấp độ bo mạch khá khó khăn và thậm chí không thể tìm thấy. Với tính năng quét ranh giới, việc kiểm tra ở cấp độ bảng cực kỳ dễ dàng

và độc lập với mạch logic bên trong chip. Quét ranh giới cũng có thể định cấu hình chế độ ATPG cho chuỗi quét của chip ở bất kỳ giai đoạn sản xuất nào.